# **Bayesian Networks based Probabilistic Approach** for Digital Circuits' Reliability

## **Usman Khalid**

Current affiliation: Sapienza University of Rome, Italy **Previous affiliation: University Technology Petronas, Malaysia**

**Student Forum**

#### Abstract

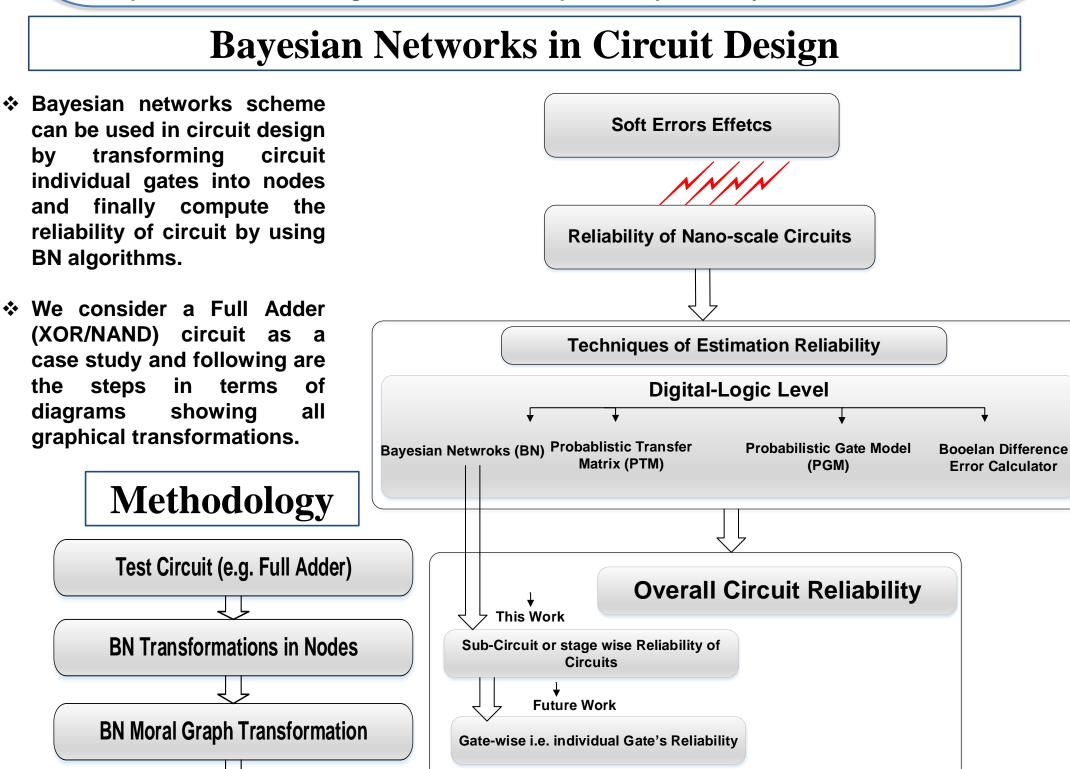

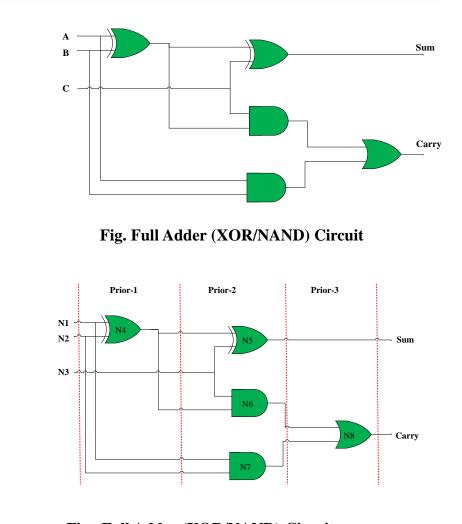

Bayesian Networks technique is widely used in artificial intelligence and image processing. The application of applying Bayesian Networks in circuit design by leveraging its exact inference schemes in order to evaluate the reliability of digital circuit. The reliability of integrated circuits degrades as MOSFET dimensions continue to scale down to nanometer dimension. The measurement of reliability of nano-scale circuits is becoming an important issue for the circuit designers. The existing reliability computation schemes can only evaluate the cumulative reliability values of circuits. The cumulative or overall reliability value does not provide the enough information to the circuit designer to apply the fault tolerant solutions unless they are aware of the reliability degradation at circuit's internal stages and cell level. This research work shows how to transform the circuits into Bayesian networks and then to evaluate the reliability of each stage of the circuit. The simulations have been done on same functionality Full Adder circuits and different functionality circuits such as Decoder and a benchmark C17 circuit. The analysis on internal stages show that the larger number of gates' stages are giving lowest reliability compare to the rest of the stages.

#### **Bayesian Networks Background Definitions**

- Bayesian networks (BN) is a kind of graphical model whose basic constituents are nodes and set of directed links between multiple nodes make directed acyclic graph [1] .

- ✤ The directed acyclic links are used to show joint probabilities between the nodes. Every Bayesian network node has a conditional probability table except their parent nodes and each parent node has an earlier probability

- We compute the error probability by assuming that our original network is error-free and \*

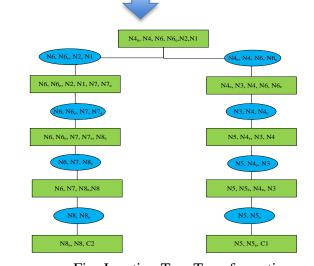

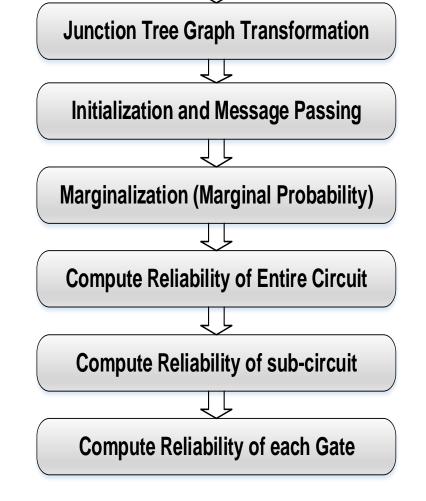

**Graphical Transformations and Methodology**

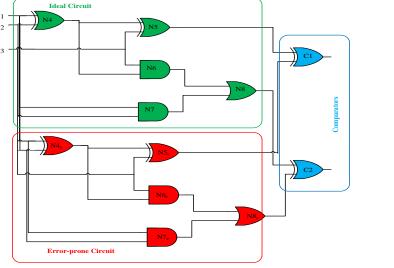

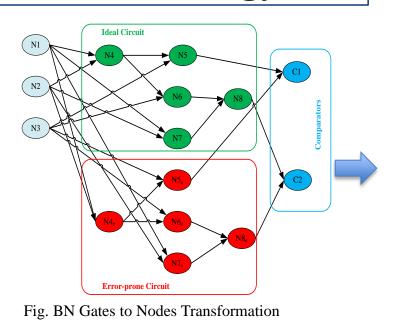

Fig. BN Conceptual Diagram

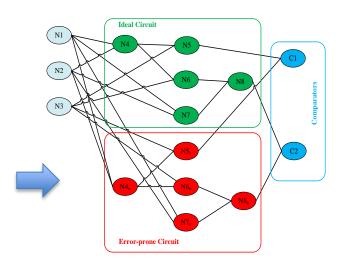

Fig. BN Moral Graph Transformation

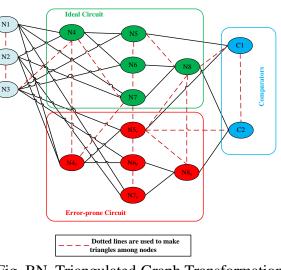

Fig. BN Triangulated Graph Transformation

making a copy of it to represent an error prone network. Error at the ith output can be represented mathematically in (1) and (2).

> $E_i = Y_i^e \otimes Y_i \quad (1)$  $P(E_i = 1) = P(Y_i^e \otimes Y_i = 1)$  (2)

$\bullet$  where;  $Y_i$  and  $Y_i^e$  are the outputs of the ideal and error prone circuits respectively. The probability of the ith output can be calculated if both error free output  $Y_i$  and error prone  $Y_i^e$ are equal to logic 1. The XOR gate is used as a comparator to compare both the original and error prone network which gives the correct output error probability.

### **Conditional Probability Tables**

Table I Digital Signal Values for Full Adder (XOR /NAND) Circuit

| Input Name     | Input values |

|----------------|--------------|

| N1             | 0 or 1       |

| N2             | 0 or 1       |

| N3             | 0 or 1       |

| N4 (N1=0,N2=0) | 0            |

| N4 (N1=0,N2=1) | 1            |

| N4 (N1=1,N2=0) | 1            |

| N4 (N1=1,N2=1) | 0            |

#### Table II CPT for Ideal Full Adder (XOR /NAND) Circuit

| Input Name     | Probability of<br>Input being 0 | Probability of Input<br>being 1 |

|----------------|---------------------------------|---------------------------------|

| N1             | P(N1=0) = 0.5                   | P(N1=1) = 0.5                   |

| N2             | P(N2=0) = 0.5                   | P(N2=1) = 0.5                   |

| N3             | P(N3=0) = 0.5                   | P(N3=1) = 0.5                   |

| N4             | P(N4=0 N1,N2)                   | P(N4=1 N1,N2)                   |

| N4 (N1=0,N2=0) | 0                               | 1                               |

| N4 (N1=0,N2=1) | 1                               | 0                               |

| N4 (N1=1,N2=0) | 1                               | 0                               |

| N4 (N1=1,N2=1) | 0                               | 1                               |

Fig. Junction Tree Transformation

| Table III CPT for Erro | or-prone Full Adder (XOR |

|------------------------|--------------------------|

| /NAN                   | D) Circuit               |

|                             | /                               |                                 |

|-----------------------------|---------------------------------|---------------------------------|

| Input Name                  | Probability of<br>Input being 0 | Probability of Input<br>being 1 |

| N1                          | P(N1=0) = 0.5                   | P(N1=1) = 0.5                   |

| N2                          | P(N2=0) = 0.5                   | P(N2=1) = 0.5                   |

| N3                          | P(N3=0) = 0.5                   | P(N3=1) = 0.5                   |

| N4                          | P(N4 <sub>e</sub> =0 N1,N2)     | P(N4 <sub>e</sub> =1 N1,N2)     |

| N4 <sub>e</sub> (N1=0,N2=0) | ε <sub>g</sub>                  | <b>1</b> - ε <sub>g</sub>       |

| N4 <sub>e</sub> (N1=0,N2=1) | <b>1-</b> ε <sub>g</sub>        | ε <sub>g</sub>                  |

| N4 <sub>e</sub> (N1=1,N2=0) | <b>1-</b> ε <sub>g</sub>        | ε <sub>g</sub>                  |

| N4 <sub>e</sub> (N1=1,N2=1) | ε <sub>g</sub>                  | <b>1-</b> ε <sub>g</sub>        |

|                             |                                 |                                 |

#### **Results**

**Table Reliability of Each Stage for Same Functionality Digital Circuits**

| Circuit Name             | Stage 1 | Stage 2 | Stage 3 | Stage 4 | Stage 5 | Stage 6 | Stage 7 |

|--------------------------|---------|---------|---------|---------|---------|---------|---------|

| Full Adder<br>(XOR/NAND) | 0.8693  | 0.8687  | 0.8723  | -       | -       | -       | -       |

| Full Adder<br>(NAND)     | 0.7576  | 0.7813  | 0.7634  | 0.7651  | 0.7746  | 0.7702  | 0.7656  |

| Full Adder<br>(Majority) | 0.8071  | 0.7305  | 0.8178  | -       | -       | -       | -       |

**Functionality Digital Circuits**

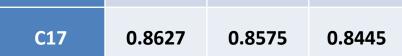

| Circuit<br>Name | Stage-1 | Stage-2 | Stage-3 | • |

|-----------------|---------|---------|---------|---|

| 2-4<br>Decoder  | 0.9500  | 0.9392  | -       |   |

Table Reliability of Each Stage for Different

The result show that the circuits having similar Boolean

functionality does not have similar location of lowest reliability stage. It depends on the number of gates in the respective stage.

The second category different functionality circuit results lead us to the same dependency as well. But the lower reliability is also dependent on the circuit structure which has been analyzed in different functionality circuits where the error-effect is propagating from primary inputs to the

**BN** Triangulated Graph Transformation

Fig. Full Adder (XOR/NAND) Circuit **Divided into sub-circuit**

internal circuitry gates and affecting the reliability of final stage.

\* So overall, the affected stages (having lower reliability values) are dependent on the larger number of gates in the respective stage.

#### Conclusion

- ✤ The graphical transformation in stage analysis using Bayesian networks gives the circuit designer an opportunity to take an in depth analysis of internal architecture of the circuit.

- ✤ The Bayesian network not only evaluates the overall reliability of a circuit but also evaluates its reliability with respect to stage location.

- ✤ This analysis shows that the affected stages are dependent on the number of gates in the respective stage and the circuit structure.

- ✤ The identification of most error-prone stage is helpful for the circuit designer who can possibly introduce fault-tolerance solutions to stages having reliability below a certain threshold. The stage analysis helps the circuit designer to take extra measures to ensure the reliability of stages having reliability below a certain threshold.

#### **Future Work**

In future work BN will be applied in order to compute the Reliability for a Gate-wise Reliability evaluation. **\*** The work is already in progress for Transistor level CMOS and FinFETs based circuits Reliability Evaluation.