Accelerating RTL Sign-off

## **A Paradigm Shift in Verification Methodology**

**Pranav Ashar Real Intent, Inc.** FMCAD, October 2016

©Copyright 2016 Real Intent Inc., Proprietary and Confidential

#### **The New Paradigm**

#### **Generic Tools**

RTL & Netlist Simulators Formal Equivalence Checker Assertion-based Formal Tool Static Timing Analyzer

|                                                                                     | <b>Targeted Solutions</b>                                                                                                            |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Untimed Paths                                                                       | Clock-Domain Crossing Checker                                                                                                        |

| Async Signals & Xings                                                               | Timing Constraint and Exception                                                                                                      |

| Timing Exceptions                                                                   | Manager and Checker                                                                                                                  |

| GALS                                                                                | Reset-Failure Tool                                                                                                                   |

| <u>Unknown Values</u>                                                               | Initialization Checker                                                                                                               |

| Lazy Initialization                                                                 | X-Safety Tool                                                                                                                        |

| Sync Reset                                                                          | Power-Ctrl Manager and Checker                                                                                                       |

| SOC Integration                                                                     | DFT Verifier                                                                                                                         |

| HW-SW Interface                                                                     | Connectivity Checker                                                                                                                 |

| Realizability                                                                       | Register Verification Tool                                                                                                           |

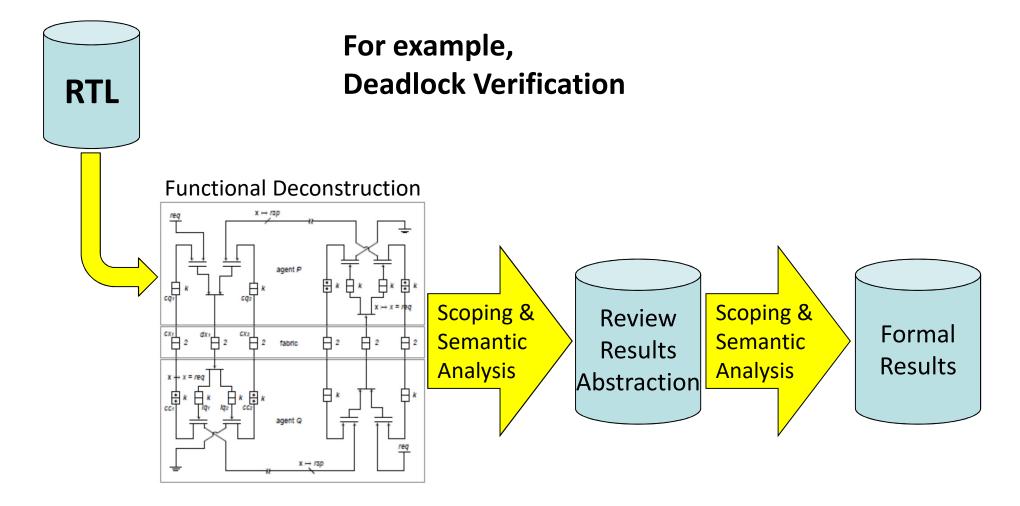

| <u>Functional Fails</u><br>Language Error<br>RTL Error<br>Interconnect Fabric Issue | RTL Code Linter<br>RTL Auto-Formal Bug Hunter<br>Security Verification Tool<br>Protocol Verifier<br>Deadlock Checker<br>FIFO Checker |

#### **New Failure Modes are Very Real**

REAL INTENT

Accelerating RTL Sign-off

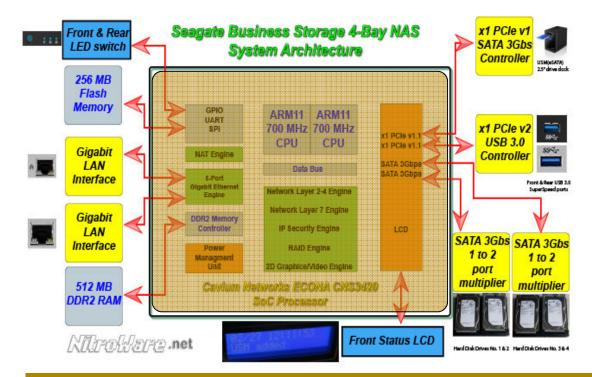

Cavium CNS3420 SoC Processor, designed specifically for Networking Devices with full offloading and hardware support for network stack, IP/SSL Security, RAID and NAT.

#### High performance

- Includes high speed ARM11 cores & caches and over 10 application acceleration engines

- Needs thorough analysis to ensure correct functionality

#### Complex

- Complex clock domain interactions

- Many reset domains

- Several asynchronous interfaces: Processor, caches, application engines, low-latency integrated memory, system and networking interfaces

#### Large: >250M gates

Needs massive capacity for the design analysis

#### High risk for silicon failure

Insidious bugs found late in the process

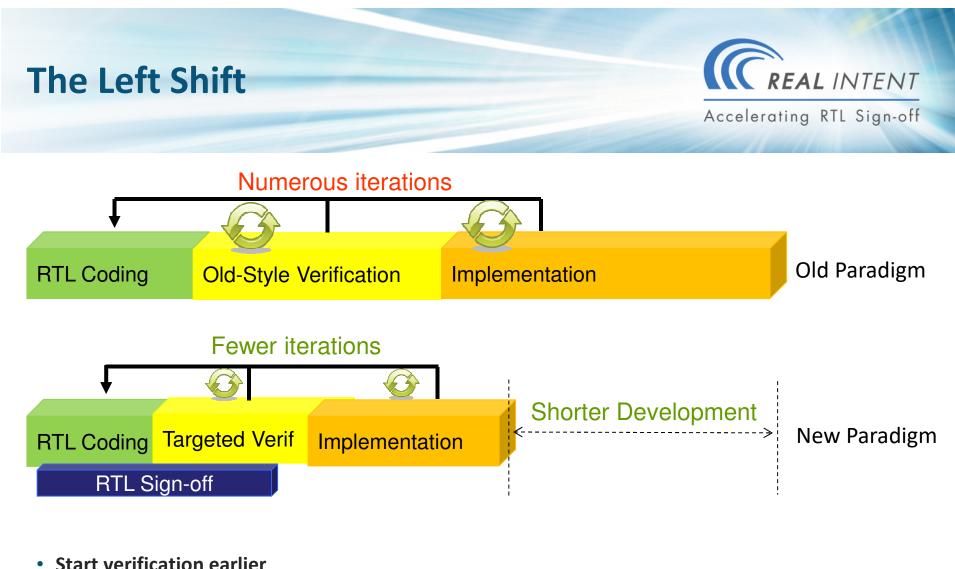

- Start verification earlier

- Compress the development cycle

- Sign-off level confidence

- Lower Cost

## Cost of a bug increases exponentially with each stage of the design process

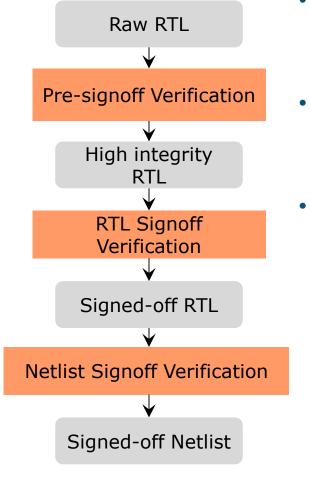

### **A Manifestation of the New Paradigm**

**REAL** INTENT

Accelerating RTL Sign-off

©Copyright 2016 Real Intent Inc., Proprietary and Confidential

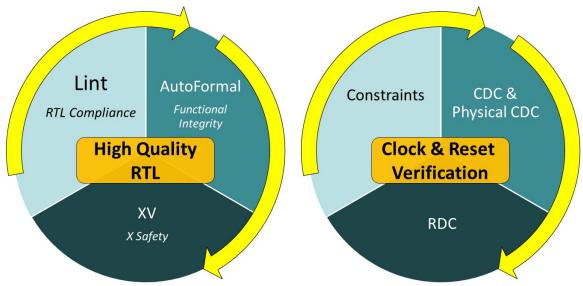

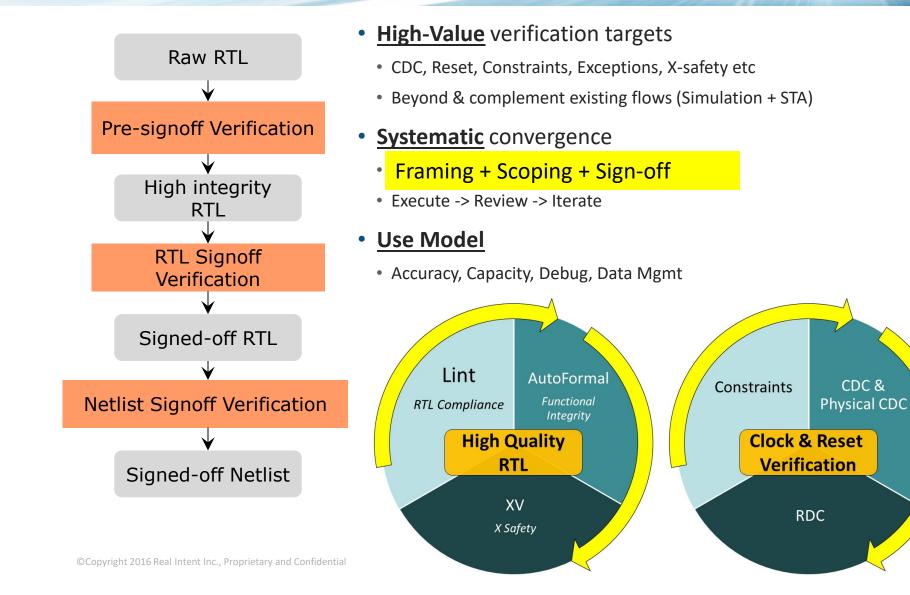

#### High-Value verification targets

- CDC, Reset, Constraints, Exceptions, X-safety etc

- Beyond & complement existing flows (Simulation + STA)

#### • Systematic convergence

- Setup + Semantic Analysis + Formal Analysis

- Execute -> Review -> Iterate

#### Use Model

• Accuracy, Capacity, Debug, Data Mgmt

### **A Manifestation of the New Paradigm**

**REAL** INTENT

## **Hidden Cost Without the New Tools:**

### **Over-design**

- Many examples:

- Extra latency on async crossings

- Paths that could be exceptions are timed in STA

- Explicitly reset every FF

- Synchronous reset where Async reset could've worked

## **Hidden Cost Without the New Tools:**

### **Over-design**

- Many examples:

- Extra latency on async crossings

- Paths that could be exceptions are timed in STA

- Explicitly reset every FF

- Synchronous reset where Async reset could've worked

REAL INTENT

## **Hidden Cost Without the New Tools:**

### **Over-design**

- Many examples:

- Extra latency on async crossings

- Paths that could be exceptions are unnecessarily timed in STA

- Explicitly reset every FF

- Synchronous reset where Async reset could've worked

REAL INTENT

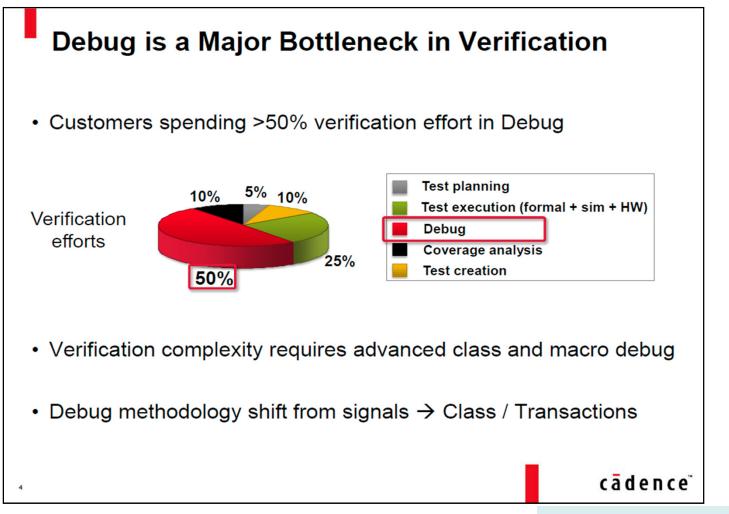

### **Debug in the New Paradigm**

Accelerating RTL Sign-off

Nick Heaton, Senior Solution Architect, Verification Futures

©Copyright 2016 Real Intent Inc., Proprietary and Confidential

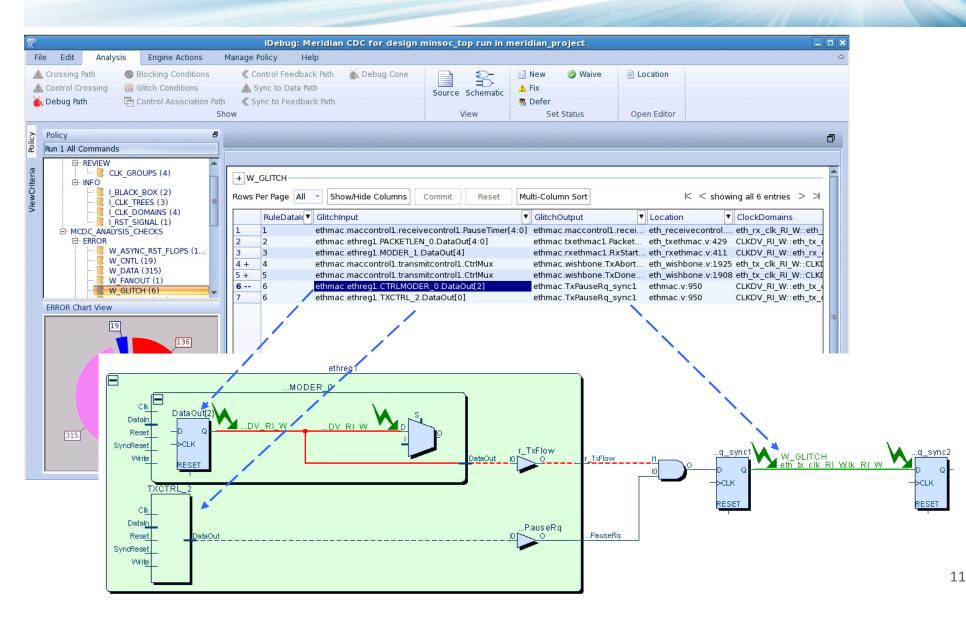

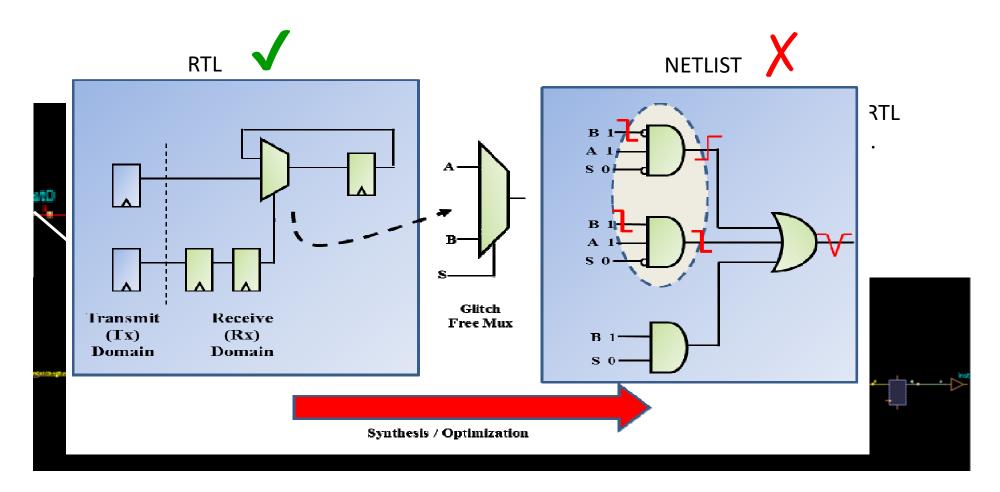

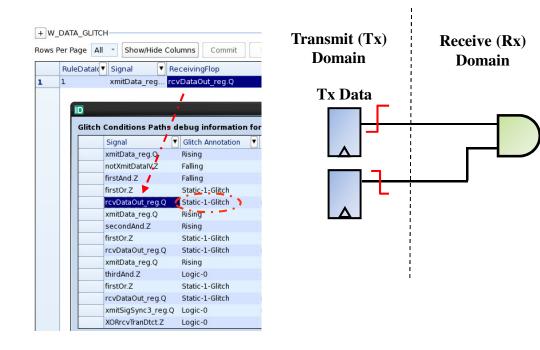

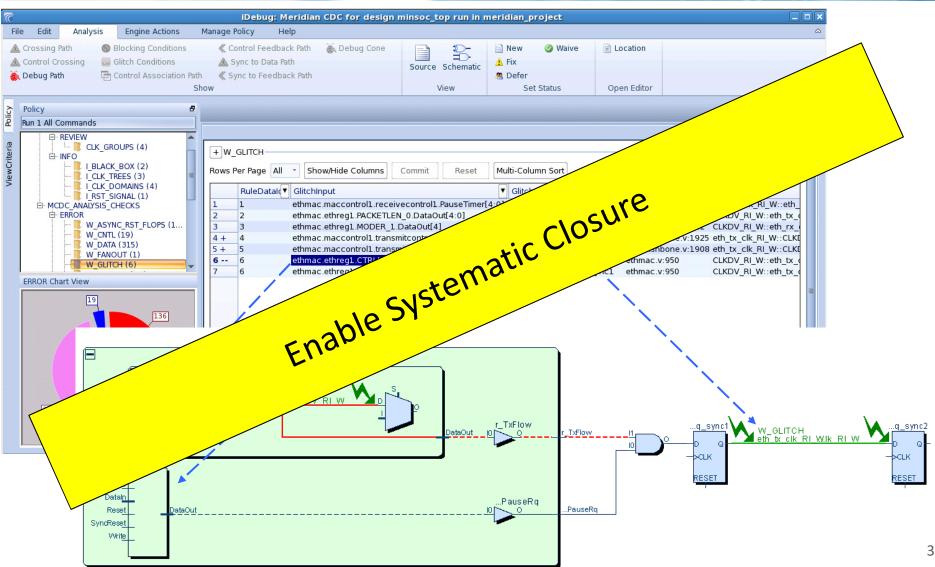

### **Tool Guides Debug Example: CDC-Glitch**

#### • Better tools => Designers take more risks

Sneaky path causes a glitch

#### • Better tools => Methodology is irrelevant

### **Overall Impact of the New Paradigm is** Salutary

- ✓ Exhaustive No test benches

- ✓ Quick start and minimal setup

- ✓ Early detection Helps prepare the design for simulation

- ✓ Sign-off on failure modes that are hard for simulation

- ✓ Address simulation's limited semantics e.g. x-prop

- Parallelizes verification: Reduced simulation

- ✓ Shorter debug cycle time

#### **Narrows the Verification Gap**

REAL INTENT

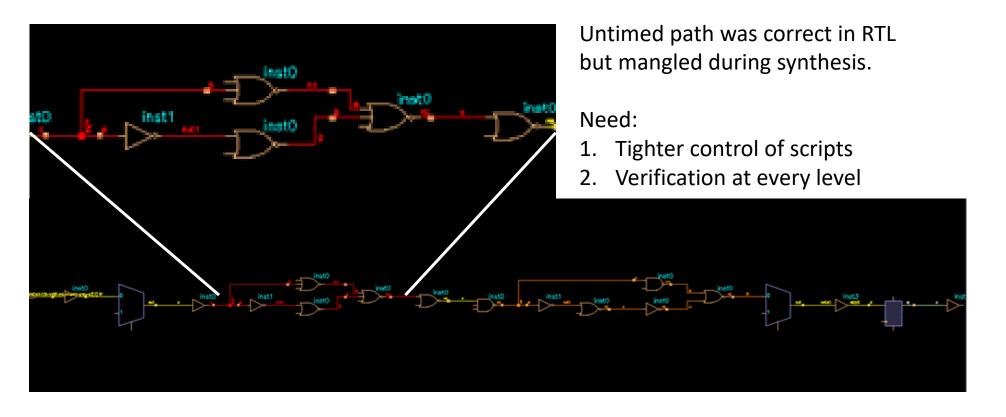

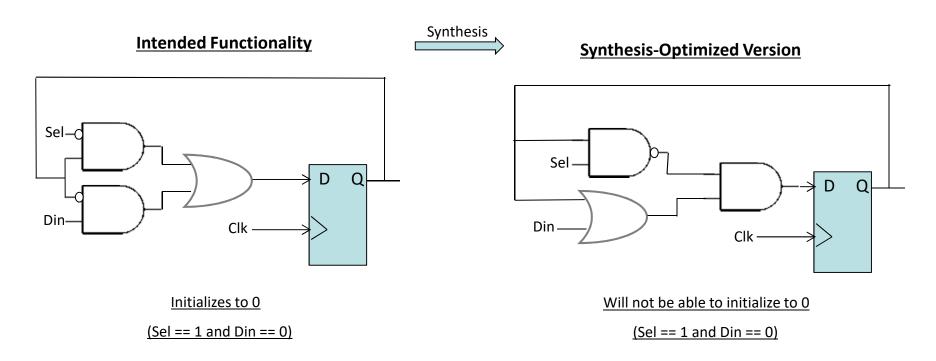

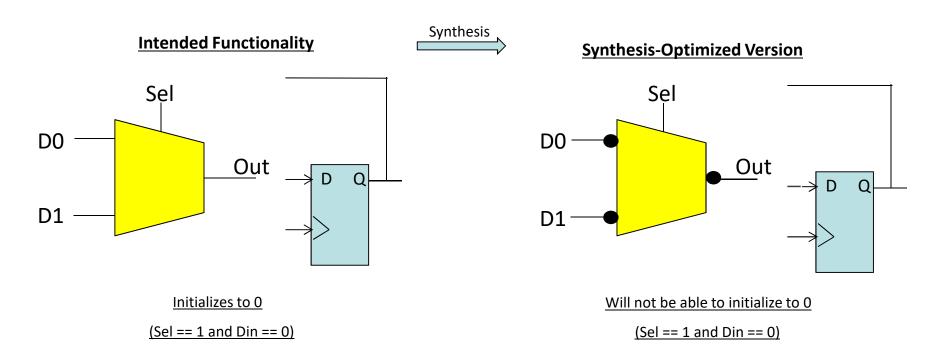

## **Problem:** Synthesis optimizes logic without knowing that X-pessimism is introduced Observed in actual netlists

## **Problem:** Synthesis optimizes logic without knowing that X-pessimism is introduced Observed in actual netlists

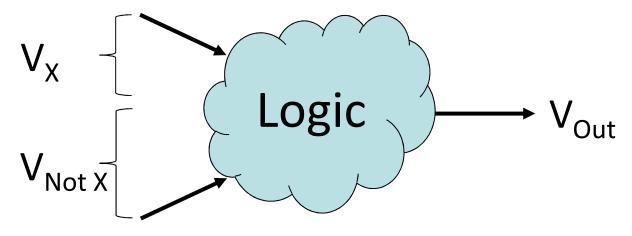

• X-pessimism analysis is conceptually a QBF problem

Is there a combination of  $V_{Not X}$  such that the value of  $V_{Out}$  is the same for all projections of  $V_X$ ?

$V_{Not\,X}$  and  $V_X$  are dynamic subsets of  $V_{In}$

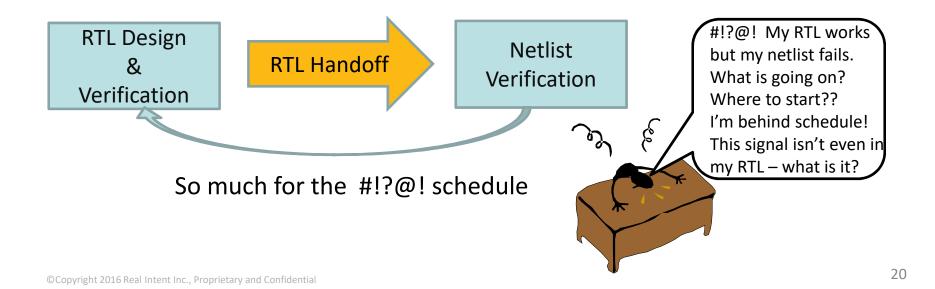

### **RTL and Netlist Simulations are Inaccurate in the Presence of X**

Optimism If (sel) D=1; sel=1'bx 1'b0 D else D=0; CLK Pessimism D=sel\*1+ ~sel\*1 1'bx D sel=1'bx Х CLK Sel=x

REAL INTENT

- Simulation behavior inaccurate

- X's cause bugs to be missed at RTL

- X's cause unnecessary additional X's at netlist

- Difficult to verify initialization in the presence of X's

- Gate level simulation bring up times are impacted by X's

- Massive productivity loss

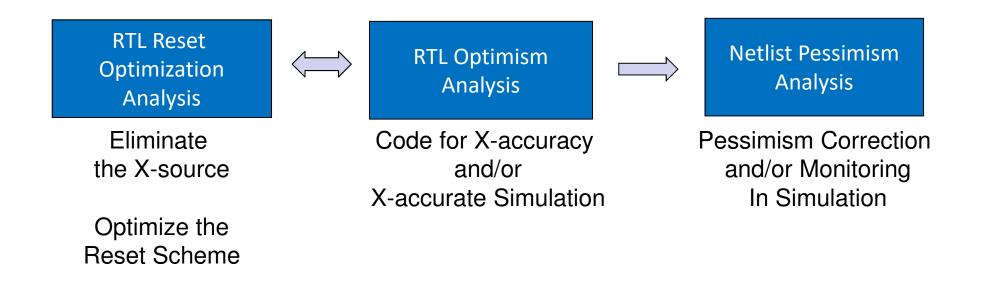

### Focus in on the Problem and Develop a Complete and Systematic Solution

- X's appear in netlist simulations that were not in RTL simulations due to pessimism and due to real X's that were masked by optimism in RTL

- Must resolve the optimism at RTL and then correct the pessimism in netlist simulations to avoid simulation differences at netlist.

REAL INTENT

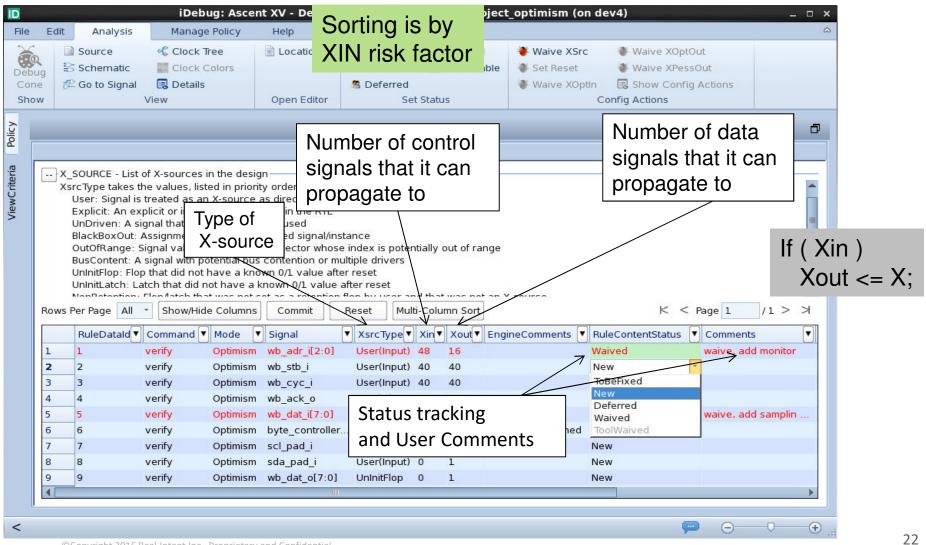

#### **Context-Smart Reporting and Debug**

REAL INTENT

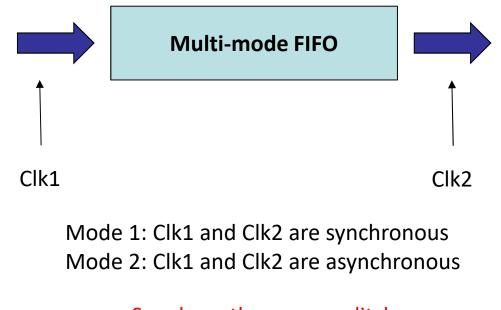

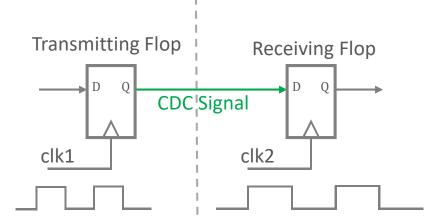

### **Another New-Paradigm Example: CDC**

## REAL INTENT

Accelerating RTL Sign-off

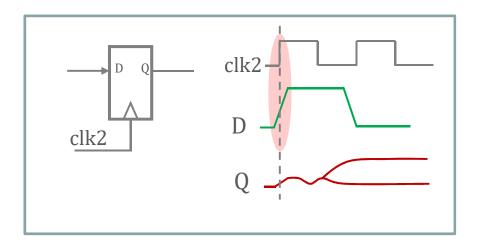

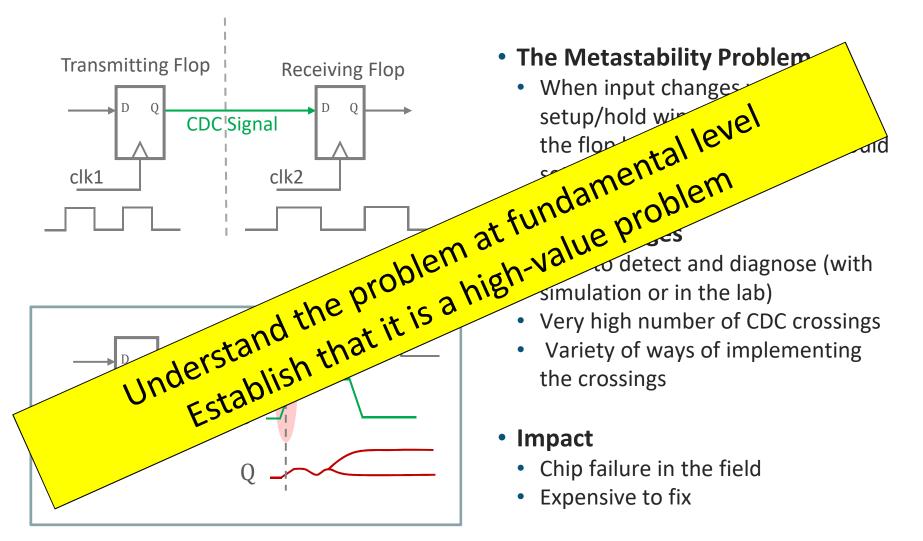

#### • The Metastability Problem

When input changes within setup/hold window, the output of the flop becomes metastable, could settle into either 0 or 1

#### • The Challenges

- Hard to detect and diagnose (with simulation or in the lab)

- Very high number of CDC crossings

- Variety of ways of implementing the crossings

#### Impact

- Chip failure in the field

- Expensive to fix

#### **Another New-Paradigm Example: CDC**

## **REAL** INTENT

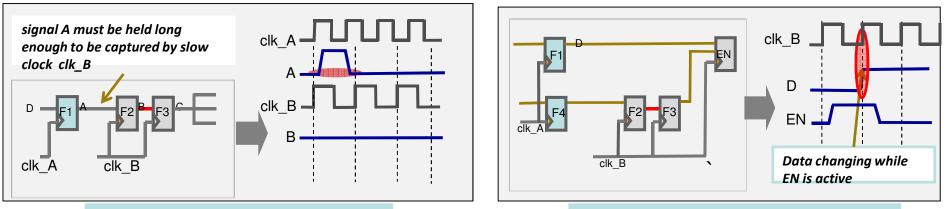

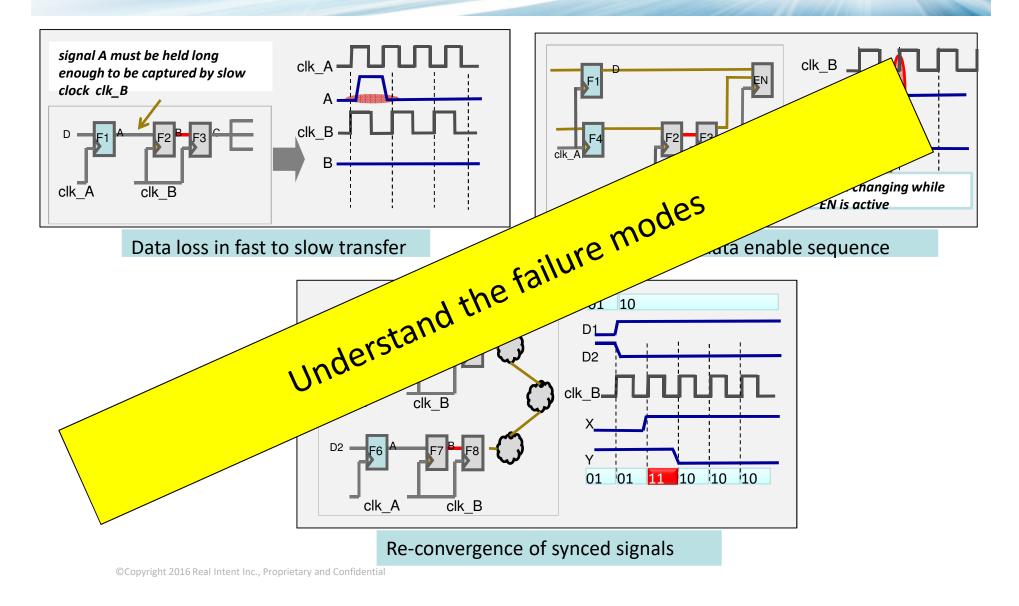

#### **Typical CDC Issues**

Accelerating RTL Sign-off

Data loss in fast to slow transfer

Improper data enable sequence

©Copyright 2016 Real Intent Inc., Proprietary and Confidential

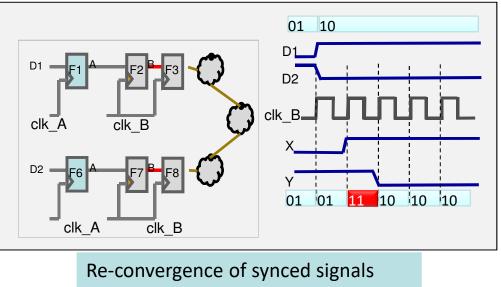

#### **Typical CDC Issues**

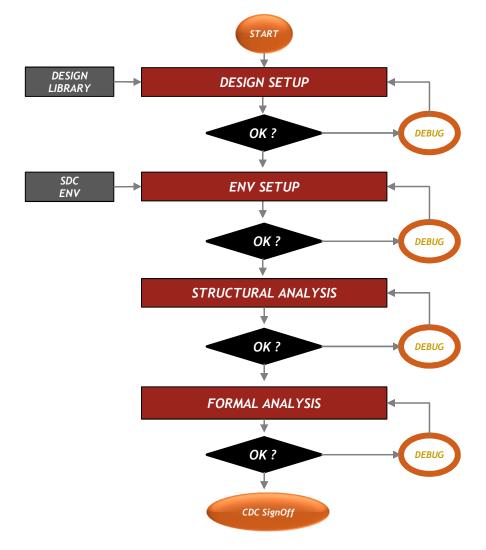

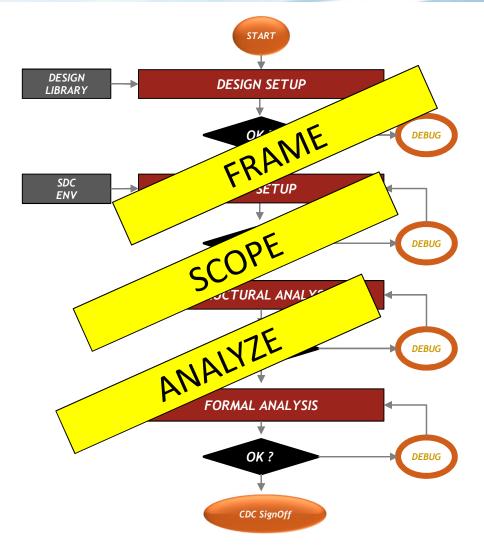

### Systematic CDC Methodology

**REAL** INTENT

Accelerating RTL Sign-off

#### Important checks Setup stage

- Missing clocks and derived clocks

- Missing clock relationships

- Missing boundary conditions

- Missing resets

- Conflicts between env specs and/or design

#### Important Checks Structural analysis

- DATA and CNTL

- Glitch

- CNTL with multiple fanouts

- Reconvergence

- Resets crossing domains

- Important Checks Formal analysis

- Data Stability

- Pulse Width

- Glitch Analysis

- GRAY CODE Checks

### Systematic CDC Methodology

REAL INTENT

Accelerating RTL Sign-off

#### Important checks Setup stage

- Missing clocks and derived clocks

- Missing clock relationships

- Missing boundary conditions

- Missing resets

- Conflicts between env specs and/or design

#### Important Checks Structural analysis

- DATA and CNTL

- Glitch

- CNTL with multiple fanouts

- Reconvergence

- Resets crossing domains

- Important Checks Formal analysis

- Data Stability

- Pulse Width

- Glitch Analysis

- GRAY CODE Checks

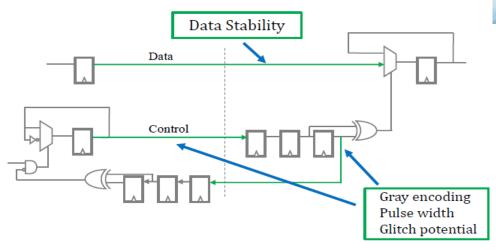

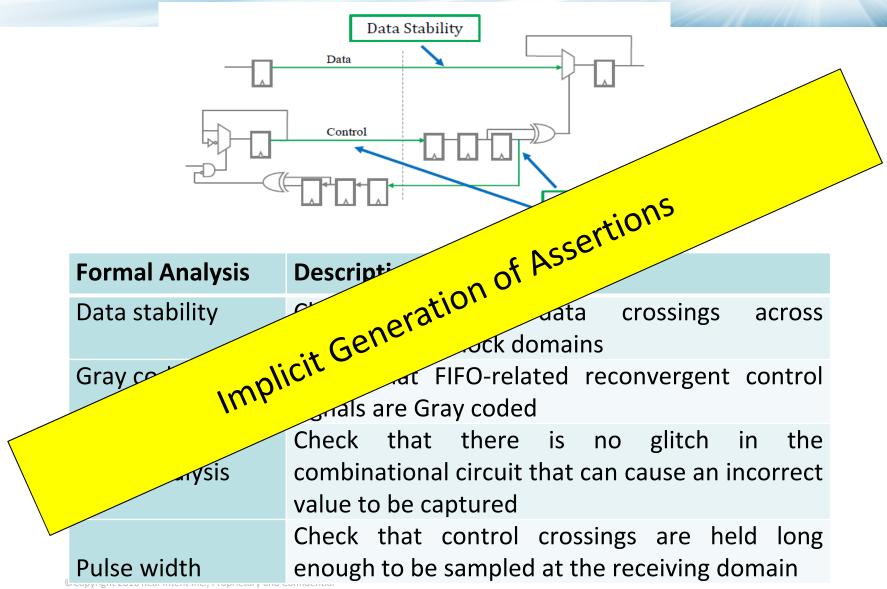

#### **Formal CDC Verification**

| Formal Analysis | Description                                                                                                 |

|-----------------|-------------------------------------------------------------------------------------------------------------|

| Data stability  | Check for safe data crossings across asynchronous clock domains                                             |

| Gray code       | Check that FIFO-related reconvergent control signals are Gray coded                                         |

| Glitch analysis | Check that there is no glitch in the combinational circuit that can cause an incorrect value to be captured |

| Pulse width     | Check that control crossings are held long<br>enough to be sampled at the receiving domain                  |

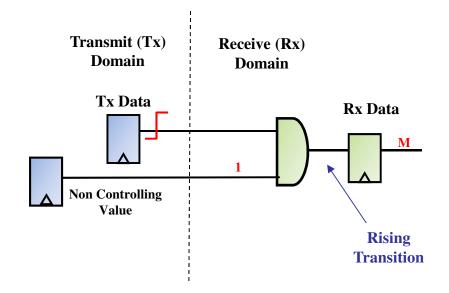

#### **Formal CDC Verification**

• Rising/Falling transition on Tx Flop lead to Rising/Falling transition on Rx Flop at next edge or Rx Clock.

• Opposing transitions on TxFlops lead to a glitch on Rx Flop

**Rx Data**

Μ

Glitch

- Parallel Formal for high throughput

- Almost 100% coverage of failure trace, pass or deep-bounded pass

- Constraints support

- Enable SVA/PSL constraints on the fly

- Extract constraint dependence

- Show in the debug

- Flexible tool control

- Fast (re)start of formal analysis iterations

- Inform users on formal run progress and completion status

Accelerating RTL Sign-off

ed

- Parallel Formal for high throughput

- Enable throughput and deep-checking in formal analysis Almost 100% coverage of failure trace, pass or deep

m users on formal run progress and completion status

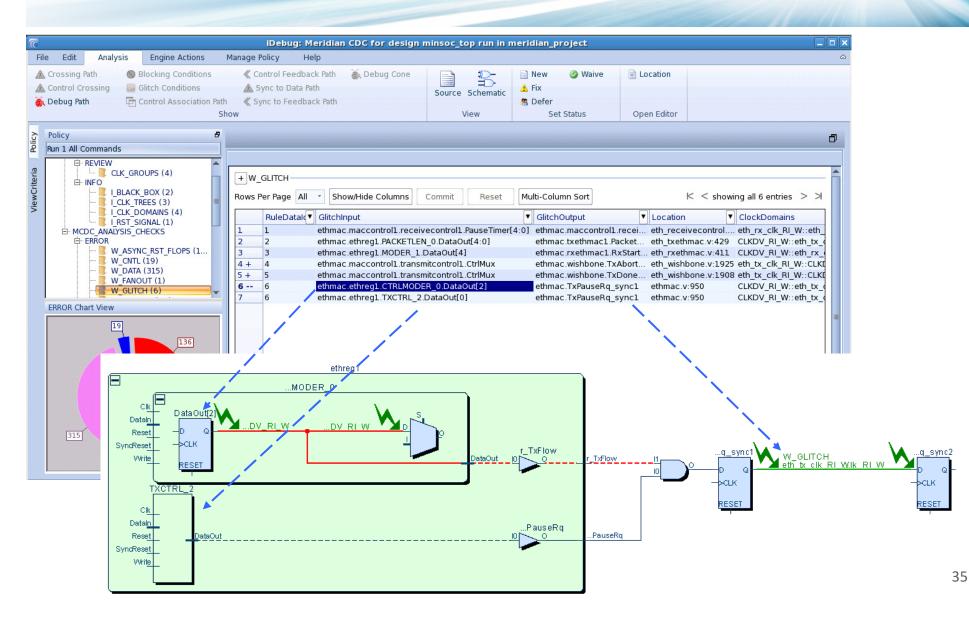

#### **Context-Smart Debug**

#### **Context-Smart Debug**

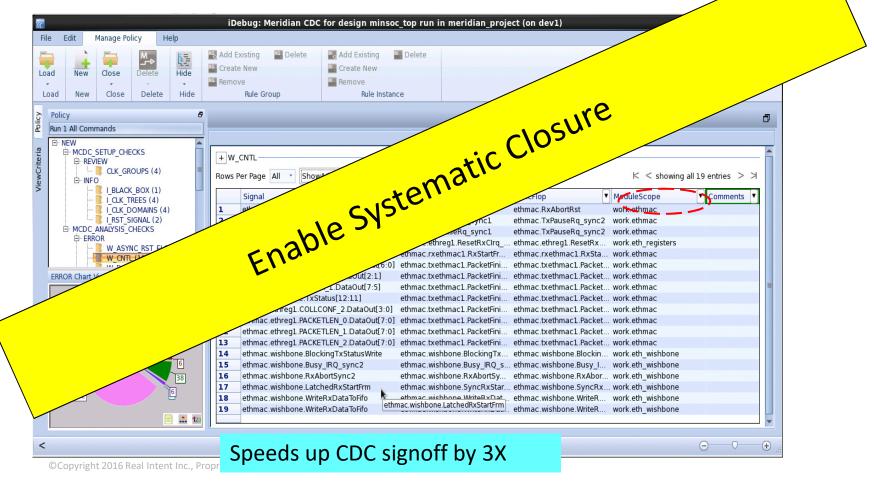

### **Scope Based Reporting: Simultaneous Chip Level and Block level results**

- ModuleScope the scope of the design violation is well contained in

- Available for all the rules

- Accessible through GUI or CLI for quick debug/SignOff

| iDebug: Meridian CDC for design minsoc_top run in meridian_project (on dev1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| File Edit Manage Policy Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ۵   |  |

| Load New Close Delete Hide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Add Existing Add Existing   Create New Create New   Remove Remove   Rule Group Rule Instance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |

| Policy<br>Run 1 All Commands<br>PNEW<br>PMCDC_SETUP_CHECKS<br>REVIEW<br>PMCDC_SETUP_CHECKS<br>REVIEW<br>PMCDC_SETUP_CHECKS<br>REVIEW<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SETUP_CHECKS<br>PMCDC_SE | + W_CNTL       Rows Per Page All        Show/Hide Columns       Commit       Reset       Multi-Column Sort       K < showing all 19 entries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Signal       ReceivingFlop       SyncFlop       ModuleScope       Comment         1       ethmac.RxAbort_wb       ethmac.RxAbortRst_sync1       ethmac.RxAbortRst       work.ethmac         2       ethmac.ethreg1.TXCTRL_2.DataOut[0]       ethmac.TxPauseRq_sync1       ethmac.TxPauseRq_sync2       work.ethmac         3       ethmac.ethreg1.CTRLMODER_0.DataOut[2]       ethmac.trxPauseRq_sync1       ethmac.TxPauseRq_sync2       work.ethmac         4       ethmac.ethreg1.SetRxCIrq_sync2       ethmac.trxelumac1tracethreg1.ResetRxCIrqethmac       ethmac.ethreg1.ResetRxwork.ethmac         5       ethmac.ethreg1.MODER_1.DataOut[4]       ethmac.txethmac1.RxStartFr       ethmac.txethmac1.RxStartFr       ethmac.txethmac1.RxStartFr         6       ethmac.ethreg1.MODER_1.DataOut[2]       ethmac.txethmac1.PacketFini       ethmac.txethmac1.Packet       work.ethmac         7       ethmac.ethreg1.MODER_1.DataOut[7:5]       ethmac.txethmac1.PacketFini       ethmac.txethmac1.Packet       work.ethmac         9       ethmac.mac.txethmac1.PacketFini       ethmac.txethmac1.Packet       work.ethmac                                                                                                                                                                                                       |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10       ethmac.ethreg1.COLLCONF_2.DataOut[3:0]       ethmac.txethmac1.Packetini       ethmac.txethmac1.Packet       work.ethmac         11       ethmac.ethreg1.PACKETLEN_0.DataOut[7:0]       ethmac.txethmac1.PacketFini       ethmac.txethmac1.Packet       work.ethmac         12       ethmac.ethreg1.PACKETLEN_1.DataOut[7:0]       ethmac.txethmac1.PacketFini       ethmac.txethmac1.Packet       work.ethmac         13       ethmac.ethreg1.PACKETLEN_2.DataOut[7:0]       ethmac.txethmac1.PacketFini       ethmac.txethmac1.Packet       work.ethmac         14       ethmac.wishbone.BlockingTxStatusWrite       ethmac.wishbone.BlockingTxStatusWrite       ethmac.wishbone.Blosy_IRQ_sync2       ethmac.wishbone.Blosy_IRQ_sync2       ethmac.wishbone.Blosy_IRQ_sync2       ethmac.wishbone.RxAbortSy       ethmac.wishbone.RxAbortSy       ethmac.wishbone.RxAbortSync         16       ethmac.wishbone.SyncRXstart.rm       ethmac.wishbone.WriteRxDataToFifo       ethmac.wishbone.VriteR       work.eth_wishbone         18       ethmac.wishbone.WriteRxDataToFifo       ethmac.wishbone.LatchedRxStartFrm       ethmac.wishbone.WriteR       work.eth_wishbone         19       ethmac.wishbone.WriteR.xDataToFifo       ethmac.wishbone.LatchedRxStartFrm       ethmac.wishbone.WriteR       work.eth_wishbone | Ţ   |  |

| <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Speeds up CDC signoff by 3X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .,: |  |

### Scope Based Reporting: Simultaneous Chip Level and Block level results

- ModuleScope the scope of the design violation is well contained in

- Available for all the rules

- Accessible through GUI or CLI for quick debug/SignOff

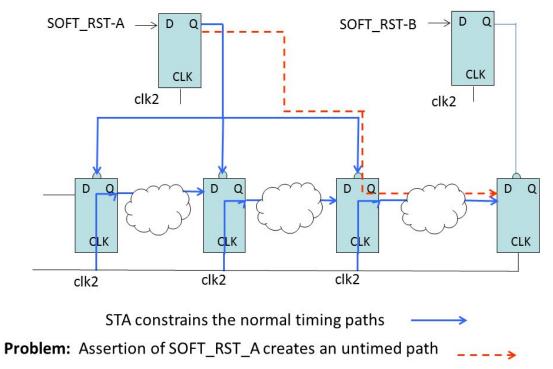

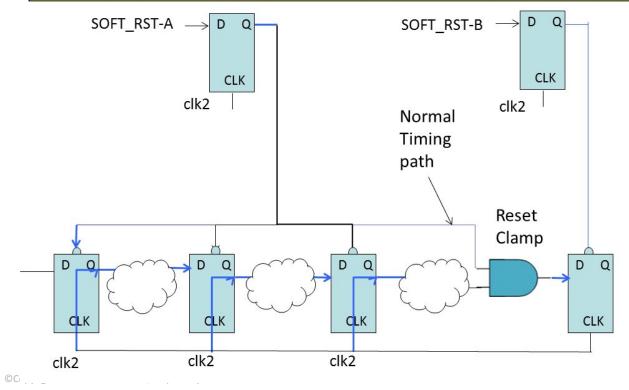

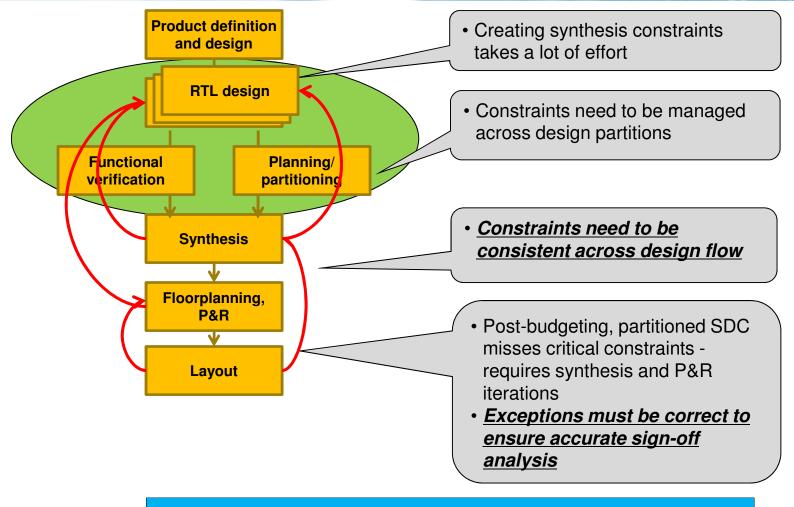

#### **The Constraints Problem**

Accelerating RTL Sign-off

#### The result – iterations and timing closure delays

©Copyright 2016 Real Intent Inc., Proprietary and Confidential

## REAL INTENT **The Constraints Problem** Accelerating RTL Sign-off Understand the problem at fundamental level **Product definition** Creating synthesis constraints Establish that it is a high-value problem Then, set up solution to Frame, Scope and Analyze Functional verification The result – iterations and timing closure delays

ht 2016 Real Intent Inc., Proprietary and Confidential

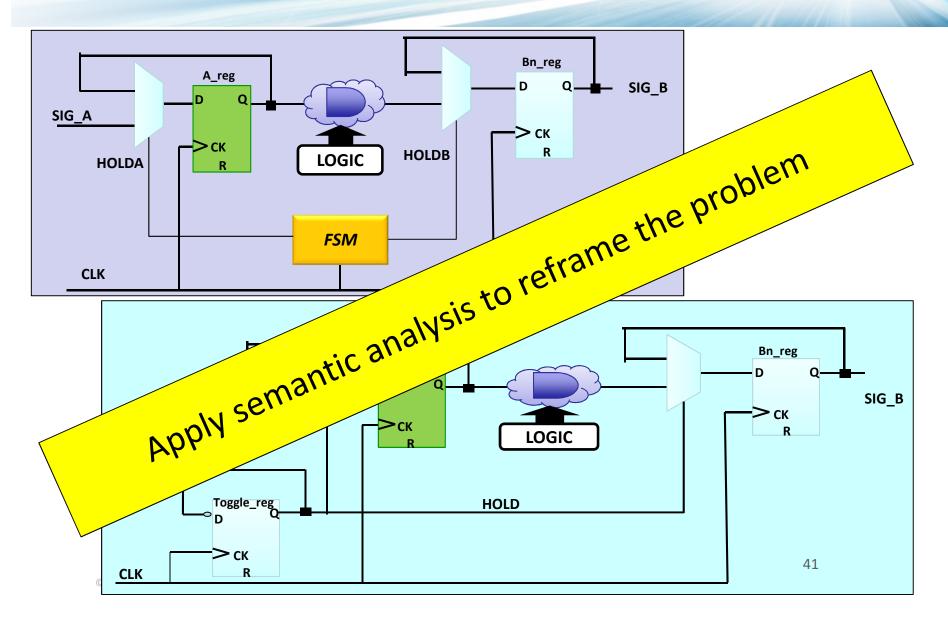

#### **Functional Analysis of Exceptions**

### Many Other Applications of the New-Paradigm Template

- Reset-Safety

- Metastability & Correlation-loss based failure modes

- Auto-Formal

- RTL functional implementation bugs

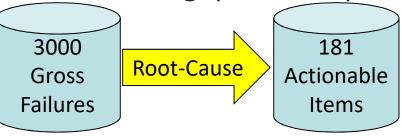

- Challenge: Identify actionable failures quickly

- Very high volume of implicit checks: Throughput vs. Depth

- Root-cause analysis is key

- Code Quality (Lint)

• A Few More ...

# Frame, Scope and Analyze Other Problems!